# AUTOMATIC GENERATION AND VERIFICATION OF INDIAN RAILWAY INTERLOCKING CONTROL TABLES

By

K. SRIRAM (312214405033)

A Project Report

Submitted to the

**Faculty of Information and Communication Engineering**

in partial fulfillment of the requirements

for the award of the degree

of

# MASTER OF ENGINEERING

IN

# **COMPUTER SCIENCE AND ENGINEERING**

ANNA UNIVERSITY

CHENNAI – 25

**JUNE 2016**

# **BONAFIDE CERTIFICATE**

Certified that this project report titled AUTOMATIC GENERATION AND VERIFICATION OF INDIAN RAILWAY INTERLOCKING CONTROL TABLES is the *bonafide* work of K. SRIRAM (312214405033) who carried out the project work under my supervision, for the fulfillment of the requirements for the award of the degree of Master of Engineering in Software Engineering. Certified further that to the best of my knowledge, the work reported herein does not form part of any other thesis or dissertation on the basis of which a degree or an award was conferred on an earlier occasion on these or any other candidates.

Place: Chennai Date:

Dr. S. Sheerazuddin

Associate Professor Department of Computer Science and Engineering SSN College of Engineering

#### COUNTERSIGNED

Head of the Department Department of Computer Science and Engineering SSN College of Engineering Kalavakkam 603 110

Submitted for the examination held on .....

Internal Examiner

External Examiner

# ABSTRACT

Generating control tables for Interlocking system in Railways is a complex task. This is generally done by the vendor, who manufactures the hardware for Indian Railways. These control tables are verified for correctness by another vendor. The problem that exists with this current method is the process followed to generate these control tables remains a black box (*i.e.*) unknown. The contribution to be made through this project is to explore this unknown process and come up with a system, that will give the correct control tables for a given layout of Railway section. For the verification of consistent routes in control table, modeling of signaling system for the given section has been done using Symbolic Model Verification (*SMV*) language and verify the SMV description using NuSMV tool.

# திட்டப்பணிச் சுருக்கம்

இருப்புப்பாதை போக்குவரத்தில் பின்னிப்பூட்டல் அமைப்பிற்கு கட்டுப்பாடு சிக்கலான பணி. அட்டவணைகளை உருவாக்குவது இந்தப் പഞ്ഞിലെ, பொதுவாக, இந்திய இருப்புபாதை போக்குவரத்து துறைக்கு வன்பொருளை தயாரித்து தரும் விற்பனையாளர்களே செய்வார்கள். இவ்விற்பனையாளர் உருவாக்கித் தரும் கட்டுப்பாடு அட்டவணைகளை சரி பார்க்க மற்றுமொரு விற்பனையாளரிடம் அளிக்கப்படுகின்றது. கட்டுப்பாடு இந்தக் சரி அட்டவணைகளை உருவாக்கவும், பார்க்கவும் கையாளப்படும் செயல்முறை ஒரு கேள்விக்குறியாக இருப்பது தான் பிரச்சனை. இந்த மறைந்திருக்கும் செயல்முறையை கட்டுப்பாடு அறியவும், சரியான உருவாக்கவும், எடுக்கப்படும் இம்முயற்சியே, அட்டவணையை இந்தத் திட்டத்தின் வாயிலாக அளிக்கப்படவிருக்கும் பங்களிப்பாகும். கட்டுப்பாடு அட்டவணைகளில் முரணற்ற தடங்களின் கலவைகளை சரி பார்க்க சமிக்ஞை அமைப்பின் மாதிரியை Symbolic Model Verification (SMV) மொழியைக் கொண்டு செய்யப்பட்டுள்ளது. இதன் பின்னர் NuSMV-யைக் கொண்டு, SMV விளக்கத்தை சரி பார்க்கப்பட்டுள்ளது.

### ACKNOWLEDGEMENT

I express my thanks to my Project Supervisor **Dr. S. Sheerazuddin**, Assistant Professor and Project Coordinator **Dr. R. S. Milton**, Professor, Department of Computer Science and Engineering, for their support and guidance.

I would like to express my heartier thanks to **Dr. Chitra Babu**, Professor and Head, Department of Computer Science and Engineering, **other faculty members and technical staff** for providing all facilities and support to meet my project requirements.

I express my sincere thanks to all the Project Review Committee members, for their timely advice.

I express my gratitude to the Principal, **Dr. S. Salivahanan and the management** of SSN College of Engineering for providing the resources and support to carry out the project successfully.

It gives me immense pleasure to express heartfelt thanks to **my parents**, **beloved friends and GOD** for helping me all the time.

**K. Sriram**

# TABLE OF CONTENTS

| A | BSTH  | RACT - | ENGLISH                                   | iii |

|---|-------|--------|-------------------------------------------|-----|

| A | BSTF  | RACT - | TAMIL                                     | iv  |

| L | IST ( | )F TAB | BLES                                      | ix  |

| L | IST ( | )F FIG | URES                                      | X   |

| 1 | BA    | CKGR   | OUND AND MOTIVATION                       | 1   |

|   | 1.1   | Introd | uction                                    | 1   |

|   | 1.2   | Organ  | ization of Report                         | 2   |

| 2 | RA    | ILWAY  | YS SIGNALLING & INTERLOCKING SYSTEM .     | 4   |

|   | 2.1   | Signal | lling concepts                            | 4   |

|   |       | 2.1.1  | Control over movement of trains           | 4   |

|   |       | 2.1.2  | Time Interval Method                      | 5   |

|   |       | 2.1.3  | Space Interval Method                     | 6   |

|   |       | 2.1.4  | Signals                                   | 6   |

|   |       | 2.1.5  | Block Working                             | 7   |

|   | 2.2   | Fixed  | Signals, Aspects & Indications            | 8   |

|   |       | 2.2.1  | Two aspect Lower Quadrant Signalling      | 9   |

|   |       | 2.2.2  | Multiple Aspect Upper Quadrant Signalling | 13  |

|   | 2.3   | Destin | nation of signals                         | 15  |

|   |       | 2.3.1  | Signals for Reception                     | 15  |

|   |       | 2.3.2  | Signals for Departure of Trains           | 16  |

|   | 2.4   | Subsic | liary Signals                             | 18  |

| Ch | apter |                                                  | Page |  |  |  |

|----|-------|--------------------------------------------------|------|--|--|--|

|    |       | 2.4.1 Shunt Signals                              | 19   |  |  |  |

|    | 2.5   | Interlocking concepts                            | 20   |  |  |  |

| 3  | BA    | SICS OF MODEL CHECKING                           | 24   |  |  |  |

|    | 3.1   | Model Checking                                   | 32   |  |  |  |

|    | 3.2   | Characteristics of Model Checking                | 37   |  |  |  |

|    |       | 3.2.1 The Model-Checking Process                 | 37   |  |  |  |

|    |       | 3.2.2 Strengths and Weaknesses                   | 42   |  |  |  |

| 4  | SU    | RVEY OF RELATED WORKS                            | 45   |  |  |  |

|    | 4.1   | Verification in UK Railways using Ladder Logic   | 45   |  |  |  |

|    | 4.2   | CSP to model and FDR to do model checking        | 45   |  |  |  |

|    | 4.3   | Interface tool to convert ASM to SMV             | 46   |  |  |  |

|    | 4.4   | Model checking using ASM                         |      |  |  |  |

|    | 4.5   | Modeling using FSM and checking using NuSMV      |      |  |  |  |

|    | 4.6   | Model checking safety-critical systems           |      |  |  |  |

|    | 4.7   | Verification using Colored Petrinets             |      |  |  |  |

|    | 4.8   | Model checking using Boolean Logic               | 48   |  |  |  |

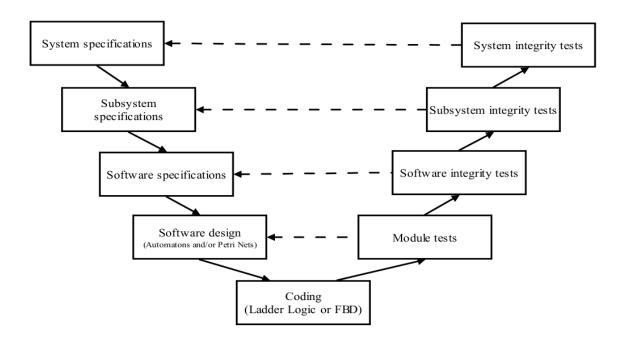

|    | 4.9   | Developing safety-critical systems using V-Model | 48   |  |  |  |

| 5  | Nu    | SMV                                              | 50   |  |  |  |

|    | 5.1   | Synchronous Systems                              | 52   |  |  |  |

|    |       | 5.1.1 Single Process Example                     | 52   |  |  |  |

|    |       | 5.1.2 Binary Counter                             | 53   |  |  |  |

|    | 5.2   | Asynchronous Systems                             | 54   |  |  |  |

|    |       | 5.2.1 Inverter Ring                              | 54   |  |  |  |

|   |                             | 5.2.2   | Mutual Exclusion                              | 57 |  |  |

|---|-----------------------------|---------|-----------------------------------------------|----|--|--|

| 6 | IM                          | PLEM    | ENTATION AND CASE STUDY                       | 59 |  |  |

|   | 6.1                         | Introdu | uction                                        | 59 |  |  |

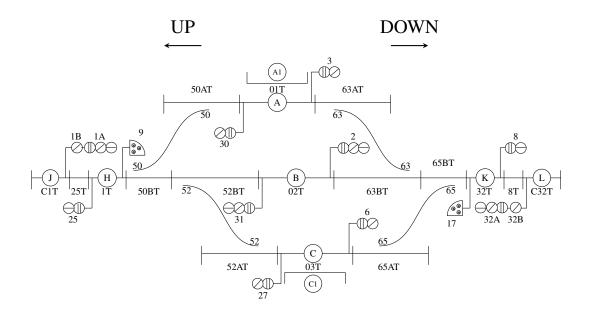

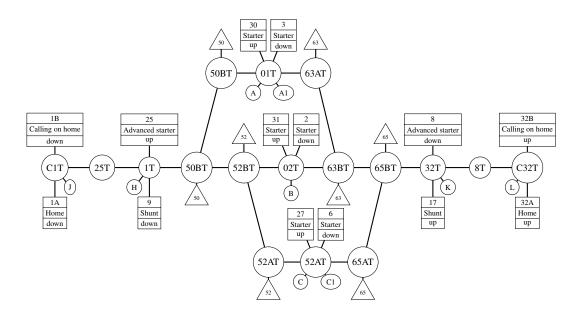

|   | 6.2                         | The ra  | ilway section layout                          | 60 |  |  |

|   | 6.3                         | Forma   | l Representation of the layout                | 61 |  |  |

|   | 6.4                         | Repres  | sentation of layout graph as a file           | 61 |  |  |

|   | 6.5                         | Functi  | ons of modules                                | 62 |  |  |

|   |                             | 6.5.1   | Routes Generator module                       | 62 |  |  |

|   |                             | 6.5.2   | Control Table Generator module                | 62 |  |  |

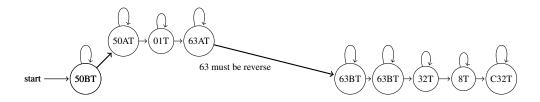

|   |                             | 6.5.3   | Consistent Routes Combination Verifier module | 63 |  |  |

|   | 6.6                         | Perfor  | mance Evaluation                              | 69 |  |  |

| 7 | CC                          | NCLU    | SION AND FUTURE WORK                          | 70 |  |  |

| A | RA                          | ILWAY   | SECTION LAYOUT AND GRAPH                      | 71 |  |  |

| B | IN                          | PUT     |                                               | 72 |  |  |

| С | M                           | )DEL (  | OF ROUTE                                      | 75 |  |  |

| D | Nu                          | SMV P   | ROGRAM FOR MODEL                              | 76 |  |  |

| E | <b>E JOURNAL DETAILS</b> 78 |         |                                               |    |  |  |

| R | EFEI                        | RENCE   | 28                                            | 79 |  |  |

# LIST OF TABLES

| 2.1 | Approaching signals used in 2-aspect signalling | 17 |

|-----|-------------------------------------------------|----|

| 2.2 | Approaching signals used in MAUQ/MACL           | 18 |

| 2.3 | Using two distant signals in approach (MACL)    | 18 |

| 2.4 | Departure signals in 2-aspect signalling        | 18 |

| 2.5 | Departure signals in M.A signalling             | 18 |

# **LIST OF FIGURES**

| 2.1 | Various Forms of Signals                                         | 7  |

|-----|------------------------------------------------------------------|----|

| 2.2 | Use Of Quadrant                                                  | 9  |

| 3.1 | Ariane-5 explosion during launch                                 | 25 |

| 3.2 | Schematic view of a posteriori system verification               | 27 |

| 3.3 | Software lifecycle and error introduction, detection, and repair |    |

|     | costs                                                            | 29 |

| 3.4 | Schematic view of the model-checking approach                    | 35 |

| 4.1 | Interlocking development lifecycle - the V-Model                 | 48 |

| A.1 | Sample layout of a railway section                               | 71 |

| A.2 | Graph representation of sample railway section layout            | 71 |

| C.1 | Model of route 1A-A through the Railway Section                  | 75 |

| C.2 | Model of route 9-A through the Railway Section                   | 75 |

# **CHAPTER 1**

#### **BACKGROUND AND MOTIVATION**

When a train enters or leaves a railway station, it is important to be sure that it does not derail and does not collide with another train. Therefore, rules have to be made for when a train can enter and leave a station. Like other railway enterprises, Indian Railways uses interlocking systems for ensuring that the safety rules are respected. Such systems are deployed for enforcing these rules on the physical objects of the stations. For instance, the track segments must be aligned correctly in position to make the train to move either straight or turn.

#### **1.1 INTRODUCTION**

A railway station or a railway section is represented as a layout diagram. This layout diagram consists of track segments connected with one another, along with signals, points and level crossings. Signals convey the information regarding operation of train or the track on which the train is set to move, to the driver. Points are the intersection of two track segments. It is used to turn a moving train from main line to loop line. Level Crossings are the control gates that co-ordinate the movement between road transport and railway without collision.

Verification tools can be classified into *interactive* and *automatic* tools. Theorem provers, at the current state of art, are not fully automatic for their usual tasks. They are driven through user interaction. As a consequence, experts are needed that are familiar with logic and the particular proof system that underlies the prover. The proof task turns out to be very time and cost intensive if it can be completed at all. Model checking tools, in contrast, do not provide a proof of correctness but rather execute an exhaustive search for errors in the state space of a model. It is an exhaustive test over all possibilities. This search can be done fully automatically. As a result, the user gets an answer that the checked requirement is either satisfied in the model or violated and, in this case, an example shows in which situation the violation may happen.

Many contributions have been made from researchers across the globe with respect to Model checking of Railways interlocking system. But their work is aligned to the Railways System in their country. As the Railways signaling system varies from country to country, it cannot be generalized for all countries. In India, there has been no publications in this field. This is due to the complexity of model checking and unpublished research work for this system. This project was suggested by Ex. Director/Indian Railways Prof. (Dr.) V Purnachandra Rao.

The objectives of this project are listed below:

- 1. Formal representation of railway section recognizable by a program.

- 2. Generation of control table entries for the railway section.

- 3. Verification of control table entries for safety conditions.

#### **1.2 ORGANIZATION OF REPORT**

This report is organized into discussion of Indian Railway's signaling system and interlocking system basics, various model checking techniques, different approaches to verify interlocking system, basics of NuSMV and about implementation of this project before concluding.

We explain the signaling system and interlocking system of Indian Railways in detail through chapter 2. In chapter 3, model checking is explained in detail. A detailed analysis of different techniques handled to verify different countries' interlocking system is given in chapter 4. NuSMV is explained in detail in chapters 5 respectively. In chapter 6, implementation details with case study is given and we conclude in chapter 7.

# **CHAPTER 2**

# **RAILWAYS SIGNALLING & INTERLOCKING SYSTEM**

In this chapter, the concepts involved in signalling and interlocking of Indian Railways are to be discussed in detail. The different types of signals and its meaning are discussed before having a look at interlocking concepts and its types.

#### 2.1 SIGNALLING CONCEPTS

Railway vehicles move on steel rail track and are provided with flanged steel wheels. The rolling of steel wheel on steel rail has the least friction and it is, therefore, one of the most efficient means of locomotion.

#### **2.1.1** Control over movement of trains

Running of flanged vehicles on the steel track has its own inherent problems unlike the road, sea or air transport where the movement is not confined to a particular track. Since the vehicles are constrained to move in a fixed railway track, they cannot be steered away as in the case of other transports. They are required to follow one another in the same direction on the length of track, as otherwise for every vehicle separate parallel paths are to be provided. This is not practical. If vehicles are expected from the opposite direction another set of diversion track is required to be provided either for overtaking vehicles moving in the same direction or for crossing the vehicles from the opposite direction. Railway locomotion, therefore, though more efficient, brings in problems of "control over movement of trains".

Basically, two types of controls could be catered for. If two separate tracks are provided for trains running in opposite directions, then one set of

control can be provided to space the movement of trains running in the same direction so that adequate "interval" is available between two consecutive trains. On the other hand, if a single track is used for movement of trains in both directions, then another set of control is required to prevent a train in the opposite direction from coming on the same track when a train is already occupying it.

#### 2.1.2 Time Interval Method

Let us take the first case of spacing of trains in the same direction. The spacing should be such that if a train stops, then, the following train driver should be able to notice it and apply brake to his train so that it stops short of the preceding train. The most important aspect is bringing to a stop from the speed at which a train is running. Where the speeds and weights are low, it is not difficult for a following train to stop short of the train ahead, which has stopped. This is how tramway operate even today, as the speed and weight are low and a tram can be stopped from its running speed without colliding with a tram in front. With higher speeds and heavier loads, as in the case of train, the distance required to stop a train is longer, and at this longer distance, the driver cannot definitely decide whether a train in front has actually stopped or not. This is the case when trains follow one another in quick succession. In actual practice, where interval between trains is longer, a following train does not see the earlier train, and the driver has to continuously guess as to where the earlier train will be. If all trains run at the same speed and are required to stop at the same place for the same duration, a certain amount of control can be exercised by having a definite time lag between the trains from one stopping place to another. This time lag should be such that the train, which has a stop, is able to reach the next stop within this time. Thus by having a time interval between trains, a certain amount of control can be

achieved. But, in the case of Railway, this is not practicable. A better method of control is called the "Space Interval Method" is adopted.

#### 2.1.3 Space Interval Method

In this method of "Control over movement", the length of track is divided into sections called "Blocks". The entry of a train into the block is controlled in such a way that only when it is free, a train can be allowed to enter it. This means that between two consecutive trains, there is a definite space interval.

This space interval or block is controlled at the entry. This controlling point should know whether the train, which had entered this space, vacated it so that another following train can be sent. Since the length of a block is beyond the normal visual range, another controlling point is set at the end of the block. This point can know whether the train has arrived and advise the controlling point at the entry. So, with the two controlling points and intercommunication, it is possible to control the entry of a train into a block only when it is vacant.

The information about the condition of this block is given by the exit point to the entry point, and the entry point transmits this information to the driver of a train. The driver of the approaching train must be able to know whether the next block is not clear, he should stop and wait. Here is where "signal" comes in to picture.

#### 2.1.4 Signals

A "Signal", therefore, is a medium to convey a particular pre-determined meaning in non-verbal form. Various methods are used to convey the meaning by "signals" in a non-verbal form as are used by Scouts, Policemen, road signs, Navy and Air Traffic Control, etc., which convey a definite informa-

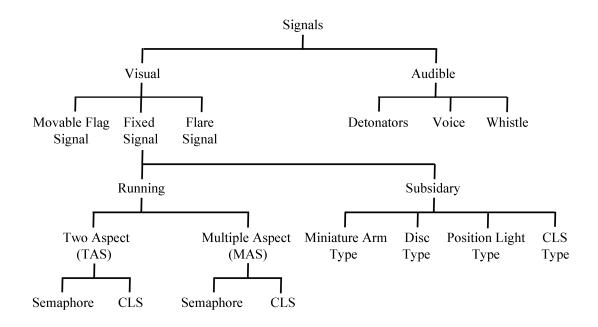

tion. The chart given in Figure 2.1, gives the various forms that could be adopted.

Figure 2.1 Various Forms of Signals

#### 2.1.5 Block Working

As explained earlier, the space interval system uses the block working wherein the entry of train onto the block section is jointly controlled by the entry and exist points of the block section. The driver is authorized to proceed into a section by the signal controlling the entry to the section. This working could be a manual block system or automatic block system. In any type before the train could be allowed to enter a section "PERMISSION" is required to be obtained from the exit end to the effect that the section is "CLEAR" of trains and the train could be permitted. Different systems of working for getting this "PERMISSION TO APPROACH" have been evolved on Indian Railways and are classified as "System of Working".

#### 2.2 FIXED SIGNALS, ASPECTS & INDICATIONS

In signals, a mention was made about the use of different types of visual and audible signals, for controlling the movement of trains in all cases. No exceptions are allowed by approved special Instructions in the following:

| (a) | Fixed signals | (c) | Detonating signals |

|-----|---------------|-----|--------------------|

|     | $\mathcal{O}$ |     | $\mathcal{O}$      |

(b) Hand signals (d) Flare signals

The definition of "Fixed Signals" as given in the General Rules is "a signal of fixed location indicating a condition affecting the movement of a train and includes a semaphore arm or disc or fixed light for use by day and a fixed light for use by night".

Semaphore signals used on the Railways are in the form of a rectangular or fish tailed arm fixed to a vertical post. The arm is kept horizontal to the post to be easily distinguishable. By this arrangement the arm can be seen from a long distance on a clear day. Whenever the signal is required to convey some information the arm can altogether be removed from the view of the driver by making the arm to disappear in a slot provided on the post, or

- (a) The arm can be made to assume a mid-way position below horizontal, or

- (b) To assume a mid-way position above horizontal, or

- (c) To assume a vertical position parallel to the extended line of the post.

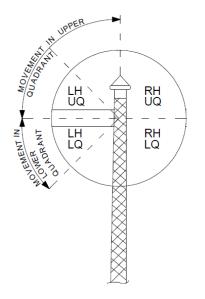

Method (a) was adopted in the early days and subsequently given up as the absence of arm due to some reason other than its entering the slot in the post conveyed wrong information. Methods (b) and (c) above could be on the Right hand side or left hand side of a Quadrant as shown below in Figure 2.2. Fixed Signals can operate on any one of the four quadrants of a circle as shown. Since 'Left hand' rule is followed in India, the "lower quadrant" and "Upper quadrant" of the left hand side is utilized in Indian Railways. Based on this principle, signals are also generally located on the left side of the track.

Figure 2.2 Use Of Quadrant

It can be seen in the Figure 2.2 that an arm in a lower quadrant can have only two positions, one at horizontal position and the other at midway position on the left-hand side. In Upper Quadrant, three positions can be obtained, i.e. one at horizontal position, one at midway position and the 3rd at vertical position in parallel with the extended line of post. Hence, we have two systems of signalling, one called "Lower Quadrant Signalling" and the other called "Upper Quadrant Signalling".

#### 2.2.1 Two aspect Lower Quadrant Signalling

(a) **Stop Signal** The semaphore arm of the stop signal is square ended, painted red with white bar parallel to the square end in front and painted

white with black bar in rear. As explained, a lower quadrant signal can show only two different positions. One is horizontal and the other lowered to midway position. They are called "aspects" of the signals. The movement of the signal arm in lower quadrant is generally adopted by countries where there is no snowfall or other external conditions which can result in the arm remaining lowered without being operated. The arm in the horizontal position will convey an aspect "stop" indicating "Stop dead". The arm lowered to midway position in the lower quadrant will convey an aspect "proceed", indicating Proceed. Semaphore arm can be seen during day and so can convey information during daytime. At night the arm will not be visible. Hence, to convey information during night, fixed light signals are used. Right from the early days, red lights were used to denote "Stop" and green lights were used for "Proceed". Red light should, therefore, be exhibited when the arm is horizontal and green light when the arm is inclined midway. A semaphore signal is a combined integrated unit with an arm and light. The horizontal position of the arm during daytime is considered as the "ON" aspect and the inclined position is the "OFF" aspect of the signal. The corresponding light red & green during night time are 'ON' and 'OFF' aspects respectively. The 'ON' aspect of a signal is also referred to as the most restrictive aspect.

(b) Warner Signal Two-aspect stop signal as explained above is the minimum required to safely space the trains. This is adequate for low speeds and low density of traffic. Safety depends on the driver seeing the signal in time under all conditions. This imposes an enormous strain on the driver who has to be constantly on the lookout, to pick up the signals. Any mistake or loss of attention can lead to serious consequences. Otherwise drivers will play safe by running at lower speeds so that he can stop at the signal even if he sees it at the last minute. With such low speeds, the time of occupying the block sections by the trains will increase, thereby reducing the number of trains per day that can be run between the block stations.

One method of overcoming this problem will be to give information in advance, or "WARNING" to the driver about the presence of stop signal ahead and the aspect displayed by the stop signal. This can be achieved in the form of another signal. This signal can precisely inform the driver that he is approaching a stop signal and also that he is required to stop or proceed. The signal which gives such warning about the condition of the stop signal ahead is called a "WARNER SIGNAL".

Since the driver is not required to stop at the warner signal, as it is only giving an advance warning about the presence of the stop signal ahead, this signal has to be different from the stop signal. The day aspect, therefore, is characterized by a fish tailed arm instead of a square ended arm. This is also a two aspect lower quadrant signal.

Since the warner signal is not a stop signal and is exhibiting red light when 'ON this should be distinguishable from a stop signal during night. This is done by mounting the arm at a lower level in the post and providing a separate additional fixed green light at 1.5 to 2.0 meters above the arm. This combination of green light above a red light distinguishes a signal as a warner signal in the 'ON' position. When the signal is lowered to midway position, the red light changes to green and the driver sees two green lights one above the other. Two precise informations are given to the driver by the Warner Signal. When the arm is horizontal during day and showing of a green light and red light below during night time indicates to the driver that he can proceed, but must be prepared to stop at the next stop signal. Similarly, the lowering of arm during day and showing of two green lights one below the other during night indicates that he can proceed and can expect all the stop signals ahead of warner for that direction are OFF and he can run through main line.

A warner signal must not be capable of being taken 'OFF' for any line other than that over which the highest speed is permitted (i.e. main line) and not until all the relevant signals have assumed 'OFF' aspect. The last of the stop signals will be the one controlling the entry of the train in the block section ahead. Even if any one of the stop signals ahead is 'ON' the warner cannot display 'OFF' aspect.

Under certain circumstances a semaphore warner signal is required to be placed on the same post of a stop signal. In such cases, the warner signal is placed below the stop signal, and the fixed green light is dispensed with.

The combination of two arms (stop and warner) on the same post gives the driver three indications in the 2-aspect lower quadrant signalling. When both the stop signal and the warner signal arms are at horizontal position and the showing of two red light one below the other gives an indication to the driver to 'stop dead' at this signal. The lowering of the stop signal above the warner or showing of a green light above a red light indicates that he can proceed past the signal with caution and be prepared to stop at the next stop signal. A third condition exists when both the arms are lowered to give two green lights one below the other. This indicates to the driver that he can proceed and can expect all the stop signals for that direction are 'OFF' and that the block section ahead is also clear. It is also made mechanically impossible to lower only the warner signal when the stop signal above it is 'ON'. In this way showing of green light below a red light is eliminated.

From the point of view of the driver, therefore, the 'ON' aspect of warner does not signify positively anything about the signals ahead whereas if such information is available, he can confidently approach the signal ahead. A system of warning about the condition of each signal by a signal in rear is, therefore, very much necessary. This leads to the concept of more than 2 aspects called "MULTIPLE ASPECT SIGNALING".

### 2.2.2 Multiple Aspect Upper Quadrant Signalling

(a) **Stop Signal** It has been mentioned in previous para that the semaphore arm can be made to assume a midway position above horizontal and also another position in parallel with the extended line of the post on the left hand upper quadrant. In this way, it is possible to obtain more than 2 aspects in the upper quadrant region and hence, it is called "Multiple Aspect" (more than 2 aspects) "Upper Quadrant" signalling as distinct from "two aspect Lower Quadrant Signalling" mentioned in previous paras.

The raising of the semaphore arm to " $45^{\circ}$  above horizontal" in the left hand upper quadrant region will convey an aspect "Caution" indicating "Proceed with caution and be prepared to stop at the next stop signal". The night aspect of the mid-way position by showing of a yellow light. The raising of the arm to 90° above horizontal in parallel with the extended line of post in a vertical position will convey an aspect "Clear" indicating "Proceed" and the next stop signal is also 'OFF'. The corresponding night aspect is the showing of a green light.

(b) **Distant Signal** As discussed in the case of 2-aspect signalling when a driver approaches the first stop signal he should be warned about its condition. Therefore, a signal similar to the warner signal in the 2-aspect signalling is also a necessity in multiple aspect upper quadrant signalling. This pre-warning signal is called a "DISTANT" signal. The term 'Distant' is used here, as this is the farthest signal from the station on the approach side. The semaphore arm will have 3 positions - horizontal,  $45^{\circ}$  above horizontal and  $90^{\circ}$  above horizontal. The arm is fishtailed similar to lower quadrant warner signal. The front side facing the train is colored yellow with a black bar parallel to the end and the backside is colored white with a black bar.

The three positions of a multiple aspect upper quadrant both of a stop signal and a distant signal are horizontal for the 'ON' position, raised to  $45^{\circ}$  above horizontal and raised to  $90^{\circ}$  above horizontal are the 'OFF' positions.

So far we have discussed two types of signals i.e. Lower Quadrant 2aspect and Multiple Aspect Upper Quadrant. The warner/distant signals are not stop signals and, therefore, "Permit" the approaching driver to pass the signal in the 'ON' position. Hence they are called "Permissive Signals". The stop signals in the 2 aspect and multiple aspect cannot be passed by the approaching driver in the 'ON' position unless and until he is specially authorized. Hence, these signals are called "Absolute Signals".

The above two types of semaphore signals are 2-aspect lower quadrant and 3-aspect upper quadrant whether permissive signals or absolute signals. The lights exhibited in the nighttime are lighted by "Kerosene Wick Lamps" or by electric lamps and they are lit only during the night time. In some areas, where the visibility of arm is very poor due to snow or fog, the night aspects are required to be lit in the day time also. The lighting of the lamps is left to the operating staff.

**Multiple Aspect Color Light Signals** Instead of having an arm by day and light by night it is preferable to have only lights as signals for both day and night and such signals are called color light signals. These are mainly used in busy suburban sections and main trunk routes, as these require electric power to operate them. Use of color light signals is essential in the electrified

sections.

At a block station it is obligatory to provide certain number of signals for controlling the movements of trains. There we require some signals to deal with the trains approaching the station and some to deal with departure of trains from the station. When more than one stop signals are used a difficulty to identify them from each other will arise. Hence it is necessary to give some name to these signals.

#### 2.3 DESTINATION OF SIGNALS

At a block station it is obligatory to provide certain number of signals for controlling the movements of trains. There we require some signals to deal with the trains approaching the station and some to deal with departure of trains from the station. When more than one stop signals are used a difficulty to identify them from each other will arise. Hence it is necessary to give some name to these signals.

#### **2.3.1** Signals for Reception

Signals, which are governing the approach and entry of trains into a station, are:

(a) **Permissive signals** A 'WARNER' in case of 2-Aspect signalling can be placed below the first stop signal or below the last stop signal or can be on a post by itself with fixed green light above. It is to warn the driver that he is approaching a stop signal or to warn him about the condition of block section ahead. In multiple aspect signalling a "DISTANT" signal is provided to indicate the driver about the condition of the stop signal ahead. If the sectional speed is 120 kmph or above, two "DISTANT" signals shall be provided. In such cases, these signals are called 'DISTANT' and 'INNER DISTANT' re-

spectively.

(b) Stop signals Minimum one permissive and one stop signal is sufficient for trains approaching a station. When stop signal is taken 'OFF' it permits the train to enter the station, this is called "HOME" signal of the station. At a station where two stop signals are provided in the approach, the first one shall be called 'OUTER' and the next shall be "HOME". In some cases where the distance between the home signal and the reception lines of the station is far away, one more stop signal may be provided, as one home signal will not be sufficient to facilitate the reception. So a stop signal provided between home and the reception lines shall be called a "ROUTING HOME".

#### 2.3.2 Signals for Departure of Trains

At the departure end of the station, the stop signals controlling the movement of trains leaving the station are:

(a) **Starter signal** Where the departure of trains is controlled by only one stop signal, it is called starter signal and is the last stop signal of the station. If two or more converging lines are there, the starter shall be placed outside all connections on the line to which it refers. Where advanced starter is also provided, the starter referring to any line is placed so as to protect the facing point or fouling mark and shall not be less than 400m in advance of the Home signal.

(b) Advanced Starter Where departure of trains is controlled by more than one stop signal, the outer most starter signal shall be the last stop signal of the station and is called "Advanced Starter". Unless approved under special instructions an "Advanced Starter" shall be placed outside all connections on the line to which it applies. It shall be placed at not less than 180m in the case of two aspect and 120m in multiple aspect signalling from the outermost point on single line and out side all connection. This distance shall be reck-oned from the starter on double line. On special nominated sections where frequent shunting involving main line takes place the "Advanced Starter" signal may be placed at a distance of full train length beyond the trailing point and the track between trailing point and the advance starter shall be track circuited. Where an advanced starter is provided, the starter referring to any line shall be placed so as to protect the first facing point or fouling mark; and shall not be less than 400m in advance of home signal.

(c) Intermediate/Routing Starter Intermediate Starter is provided between starter & advanced starter where necessary, and is placed in rear of the point, which it protects.

We have seen the aspects and indications of an individual signal. The following aspect sequence charts give us the various combinations of signals, their aspect and indications conveyed to the driver of an approaching train. (Using light aspects)

| Warner | Outer | Home | Home Indication                                              |  |

|--------|-------|------|--------------------------------------------------------------|--|

| R      | R     | R    | Stop at outer signal                                         |  |

| R      | G     | G    | Enter the station. Stop at starter of concerned line if 'ON' |  |

| G      | G     | G    | Run through via main line all signals ahead are 'OFF'        |  |

Table 2.1 Approaching signals used in 2-aspect signalling

| Distant | Home | Indication                                   |

|---------|------|----------------------------------------------|

| Y       | R    | Stop at home signal                          |

| YY      | Y    | Enter on loop line. Stop at starter if 'ON'. |

| G       | Y    | Enter on main line. Stop at starter.         |

| G       | G    | Run through via main line                    |

Table 2.2 Approaching signals used in MAUQ/MACL

| Distant | Inner Distant | Home | Indication                                  |

|---------|---------------|------|---------------------------------------------|

| YY      | Y             | R    | Stop at home                                |

| YY      | YY            | Y    | Enter on loop line. Stop at starter if 'ON' |

| G       | YY            | Y    | Enter on main line. Stop at starter.        |

| G       | G             | G    | Run through via main line                   |

Table 2.3 Using two distant signals in approach (MACL)

| Starter | Advanced<br>Starter | Indication                  |

|---------|---------------------|-----------------------------|

| R       | R                   | Stand in rear of starter    |

| G       | R                   | Shunt upto advanced starter |

| G       | G                   | Proceed line is clear       |

Table 2.4 Departure signals in 2-aspect signalling

| Starter | Advanced<br>Starter | Indication                  |  |

|---------|---------------------|-----------------------------|--|

| R       | R                   | Stand in rear of starter    |  |

| Y       | R                   | Shunt upto advanced starter |  |

| Y/G     | G                   | Proceed line is clear       |  |

Table 2.5 Departure signals in M.A signalling

# 2.4 SUBSIDIARY SIGNALS

In the previous chapters we have seen the signals authorizing the drivers to enter the station from a block section by the use of reception signals; and enter the block section from the station by the use of departure signals. These signals were, therefore, being used for reception and despatch of running trains. As per definition a "Running train" is a train which has started under an authority to proceed and has not completed its journey whereas "a train" is an engine with or without vehicles attached or self propelled vehicle with or without a trailer which cannot be readily lifted off the track. The signals, which control the movement of trains within the station section, are to be differentiated and convey different indication to the driver. These signals are (a) Shunt signals and (b) Calling on signals and are called "SUBSIDIARY SIGNALS".

#### 2.4.1 Shunt Signals

- (a) Shunt signals authorize movement only at such slow speeds as to be able to stop short of any obstruction and control shunting movements.

- (b) Shunt signals can be placed on a separate post by itself close to the ground or can be placed below a stop signal other than the first and last stop signal of a station.

- (c) More than one shunt signal may be placed on the same post in which case the top-most signal shall apply to the extreme left hand line and the second shunt signal from the top shall apply to the next line from the left and so on.

- (d) Shunt signal when taken 'OFF' authorities the driver to draw ahead with caution even though the stop signal, if any, above it is at 'ON' position, and

- (e) The shunt signal shall be either

- (i) Disc type shunt signal.

- (ii) Position light shunt signal.

- (f) Under special instructions, a shunt signal may be a miniature arm.

- (g) When a shunt signal is placed below a stop signal, it shall show no light in the "ON" position.

#### 2.5 INTERLOCKING CONCEPTS

In order to ensure that the signalling system never provides unsafe (conflicting) signals and the points are not set for more than one train that might end up proceeding on to the same section of track and hence suffering a collision, various schemes have been developed to coordinate the settings of the points and the signals within the region controlled by a signalbox or signal cabin.

**Mechanically operated interlocking:** The most prevalent systems today (2003) are still mechanical interlocking schemes that coordinate the positions of the levers controlling the points with the signals governing that section of track and connected branches, loops, or sidings.

For instance, in one common scheme, a key that allows setting the points for a route has to be obtained from the block instrument, and as long as the key is removed the instrument cannot be set to provide Line Clear for a conflicting route. The wires that operate signals, and the rods that control points, are all interconnected in the lever frames at the signal cabins so that they are literally 'interlocked' - the position of one lever or key physically obstructs the movements of other levers and keys which control points or signals that can be set in conflicting ways. **Manually operated interlocking:** This is a form of mechanical interlocking as well, but relies on the signalman to move about from one set of points and signals to another carrying with him the keys used to operate them. At small stations and on less busy branch lines various forms of manually operated mechanical interlocking are still [11/03] widespread. At points controlling catch sidings in hilly areas, often the interlocking is manual where the driver has to use a key provided by the stationmaster or signalman of the last station before the siding - the key is inserted into the interlock box which notifies the signal cabin and the points are then set for the main line and the signal is pulled off, giving the train authority to proceed. (This system is common in many hilly areas, although busier lines with catch sidings are being provided with automatically operating delayed signals where the points are controlled by a timer and are set to the main line only after the train has halted for the prescribed period of time.)

A common system in use was **Sequential Key Interlocking**, which saved on the installation of point rodding and instead relied on the signalman walking over with a key to lock or unlock points. As an example, consider a station with a main line and a loop line. To receive a train on the main line, a key is inserted into the signal frame in the cabin or platform, which allows the Outer and Home signals of the station to be pulled off.

In order to receive a train on the loop line instead, the key is used as before to pull off the Outer signal, but the Home is kept at danger. Instead, when the train has stopped at the Home signal the key is removed and taken to the facing points for the loop. The same key unlocks the points so they can be set for the loop; it also releases another key which has to be taken back and inserted in the signal frame at the platform to pull off the Home signal to let the train advance on to the loop. The mechanism was such that only one of these two keys could be released at once; the second key did not allow the operation of the Outer signal, and it had to be taken back to the facing points of the loop in order to release the first key.

**Electrically operated interlocking:** In the more advanced electrical or electronic interlocking schemes, the points and signals are worked from one integrated mechanism in a signal cabin which features a display of the entire track layout with indications of sections that are occupied, free, set for reception or dispatch, etc. The interlocking is accomplished not by mechanical devices but by electrical circuitry - relays and switches in older electrical or electro pneumatic systems, and computerized circuits in the newer electronic systems.

**Panel Interlocking**(PI) is the system used in most medium-sized stations on IR. In this, the points and signals are worked by individual switches that control them. **Route Relay Interlocking**(RRI) is the system used in large and busy stations that have to handle high volumes of train movements. In this, an entire route through the station can be selected and all the associated points and signals along the route can be set at once by a switch for receiving, holding, blocking, or dispatching trains.

The description of the possible routes that can be set, and the corresponding dispositions of points and signals are found in the **locking table** and **selection table** for a station. The locking table lists the signals and points controlled; the levers at signal boxes (or control panels at control centres) which operate various signals and points; which signals and points are locked (and in what position) when other signals are pulled off or points set; which track circuits are clear or occupied; etc. The requirement for having signalling system, different possible signalling systems with their underlying concepts and the indication of signals based on their location was discussed in this chapter. Also, the concepts of interlocking system and its types were discussed in detail.

# **CHAPTER 3**

### **BASICS OF MODEL CHECKING**

In the previous chapter we discussed about the various signalling concepts and the different techniques involved in interlocking system. This chapter deals about the importance and purpose of doing model checking before building any system either hardware or software after designing its prototype. There are also few examples which show the problems of not using model checking. The flow, architecture and process of model checking are also discussed.

Our reliance on the functioning of ICT systems (Information and Communication Technology) is growing rapidly. These systems are becoming more and more complex and are massively encroaching on daily life via the Internet and all kinds of embedded systems such as smart cards, hand-held computers, mobile phones, and high-end television sets. Services like electronic banking and teleshopping have become reality. The daily cash flow via the Internet is about  $10^{12}$  million US dollars. Roughly 20% of the product development costs of modern transportation devices such as cars, high-speed trains, and airplanes is devoted to information processing systems.

ICT systems are universal and omnipresent. They control the stock exchange market, form the heart of telephone switches, are crucial to Internet technology, and are vital for several kinds of medical systems. Our reliance on embedded systems makes their reliable operation of large social importance. Besides offering a good performance in terms like response times and processing capacity, the absence of annoying errors is one of the major quality indications. It is all about money. We are annoyed when our mobile phone malfunctions, or when our video recorder reacts unexpectedly and wrongly to our issued commands. These software and hardware errors do not threaten our lives, but may have substantial financial consequences for the manufacturer. Correct ICT systems are essential for the survival of a company. Dramatic examples are known. The bug in Intels Pentium II floating-point division unit in the early nineties caused a loss of about 475 million US dollars to replace faulty processors, and severely damaged Intels reputation as a reliable chip manufacturer. The software error in a baggage handling system postponed the opening of Denvers airport for 9 months, at a loss of 1.1 million US dollar per day. Twenty-four hours of failure of the worldwide online ticket reservation system of a large airplane company will cause its bankruptcy because of missed orders.

Figure 3.1 Ariane-5 explosion during launch

It is all about safety: errors can be catastrophic too. The fatal defects in the control software of the Ariane-5 missile (Figure 3.1), the Mars Pathfinder,

and the airplanes of the Airbus family led to headlines in newspapers all over the world and are notorious by now. Similar software is used for the process control of safety-critical systems such as chemical plants, nuclear power plants, traffic control and alert systems, and storm surge barriers. Clearly, bugs in such software can have disastrous consequences. For example, a software flaw in the control part of the radiation therapy machine Therac-25 caused the death of six cancer patients between 1985 and 1987 as they were exposed to an overdose of radiation.

The increasing reliance of critical applications on information processing leads us to state:

The reliability of ICT systems is a key issue in the system design process.

The magnitude of ICT systems, as well as their complexity, grows apace. ICT systems are no longer standalone, but are typically embedded in a larger context, connecting and interacting with several other components and systems. They thus become much more vulnerable to errors the number of defects grows exponentially with the number of interacting system components. In particular, phenomena such as concurrency and nondeterminism that are central to modeling interacting systems turn out to be very hard to handle with standard techniques. Their growing complexity, together with the pressure to drastically reduce system development time ("time-to-market"), makes the delivery of low-defect ICT systems an enormously challenging and complex activity.

#### Hardware and Software Verification

System verification techniques are being applied to the design of ICT systems in a more reliable way. Briefly, system verification is used to estab-

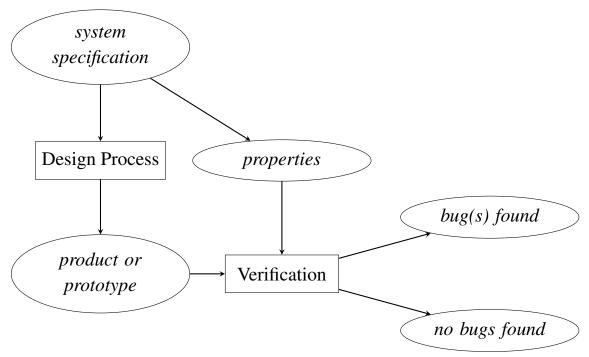

Figure 3.2 Schematic view of a posteriori system verification

lish that the design or product under consideration possesses certain properties. The properties to be validated can be quite elementary, e.g., a system should never be able to reach a situation in which no progress can be made (a deadlock scenario), and are mostly obtained from the systems specification. This specification prescribes what the system has to do and what not, and thus constitutes the basis for any verification activity. A defect is found once the system does not fulfill one of the specifications properties. The system is considered to be "correct" whenever it satisfies all properties obtained from its specification. So correctness is always relative to a specification, and is not an absolute property of a system. A schematic view of verification is depicted in Figure 3.2.

**Software verification:** Peer reviewing and testing are the major software verification techniques used in practice.

A *peer review* amounts to a software inspection carried out by a team of software engineers that preferably has not been involved in the development of the software under review. The uncompilable code is not executed, but analyzed completely statically. Empirical studies indicate that peer review provides an effective technique that catches between 31% and 93% of the defects with a median around 60%. While mostly applied in a rather ad hoc manner, more dedicated types of peer review procedures, e.g., those that are focused at specific error-detection goals, are even more effective. Despite its almost complete manual nature, peer review is thus a rather useful technique. It is therefore not surprising that some form of peer review is used in almost 80% of all software engineering projects. Due to its static nature, experience has shown that subtle errors such as concurrency and algorithm defects are hard to catch using peer review.

*Software testing* constitutes a significant part of any software engineering project. Between 30% and 50% of the total software project costs are devoted to testing. As opposed to peer review, which analyzes code statically without executing it, testing is a dynamic technique that actually runs the software. Testing takes the piece of software under consideration and provides its compiled code with inputs, called tests. Correctness is thus determined by forcing the software to traverse a set of execution paths, sequences of code statements representing a run of the software. Based on the observations during test execution, the actual output of the software is compared to the output as documented in the system specification. Although test generation and test execution can partly be automated, the comparison is usually performed by human beings. The main advantage of testing is that it can be applied to all sorts of software, ranging from application software (e.g., ebusiness software) to compilers and operating systems. As exhaustive testing of all execution paths is practically infeasible; in practice only a small subset of these paths is treated. Testing can thus never be complete. That is to say, testing can only show the presence of errors, not their absence. Another problem with testing is to determine when to stop. Practically, it is hard, and mostly impossible, to indicate the intensity of testing to reach a certain defect density - the fraction of defects per number of uncommented code lines.

Studies have provided evidence that peer review and testing catch different classes of defects at different stages in the development cycle. They are therefore often used together. To increase the reliability of software, these software verification approaches are complemented with software process improvement techniques, structured design and specification methods (such as the Unified Modeling Language), and the use of version and configuration management control systems. Formal techniques are used, in one form or another, in about 10% to 15% of all software projects.

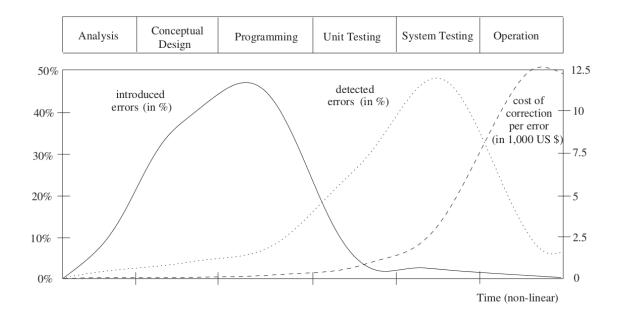

Figure 3.3 Software lifecycle and error introduction, detection, and repair costs

*Catching software errors: the sooner the better.* It is of great importance to locate software bugs. The slogan is: the sooner the better. The costs of repairing a software flaw during maintenance are roughly 500 times higher than a fix in an early design phase (see Figure 3.3). System verification should thus take place early stage in the design process.

About 50% of all defects are introduced during programming, the phase in which actual coding takes place. Whereas just 15% of all errors are detected in the initial design stages, most errors are found during testing. At the start of unit testing, which is oriented to discovering defects in the individual software modules that make up the system, a defect density of about 20 defects per 1000 lines of (uncommented) code is typical. This has been reduced to about 6 defects per 1000 code lines at the start of system testing, where a collection of such modules that constitutes a real product is tested. On launching a new software release, the typical accepted software defect density is about one defect per 1000 lines of code lines.

Errors are typically concentrated in a few software modules about half of the modules are defect free, and about 80% of the defects arise in a small fraction (about 20%) of the modules and often occur when interfacing modules. The repair of errors that are detected prior to testing can be done rather economically. The repair cost significantly increases from about \$1000 (per error repair) in unit testing to a maximum of about \$12,500 when the defect is demonstrated during system operation only. It is of vital importance to seek techniques that find defects as early as possible in the software design process: the costs to repair them are substantially lower, and their influence on the rest of the design is less substantial. Hardware verification: Preventing errors in hardware design is vital. Hardware is subject to high fabrication costs; fixing defects after delivery to customers is difficult, and quality expectations are high. Whereas software defects can be repaired by providing users with patches or updates nowadays users even tend to anticipate and accept this hardware bug fixes after delivery to customers are very difficult and mostly require refabrication and redistribution. This has immense economic consequences. The replacement of the faulty Pentium II processors caused Intel a loss of about \$475 million. Moore's law the number of logical gates in a circuit doubles every 18 months has proven to be true in practice and is a major obstacle to producing correct hardware. Empirical studies have indicated that more than 50% of all ASICs (Application-Specific Integrated Circuits) do not work properly after initial design and fabrication. It is not surprising that chip manufacturers invest a lot in getting their designs right. Hardware verification is a well-established part of the design process. The design effort in a typical hardware design amounts to only 27% of the total time spent on the chip; the rest is devoted to error detection and prevention.

*Hardware verification techniques*. Emulation, simulation, and structural analysis are the major techniques used in hardware verification.

*Structural analysis* comprises several specific techniques such as synthesis, timing analysis, and equivalence checking.

*Emulation* is a kind of testing. A reconfigurable generic hardware system (the emulator) is configured such that it behaves like the circuit under consideration and is then extensively tested. As with software testing, emulation amounts to providing a set of stimuli to the circuit and comparing the generated output with the expected output as laid down in the chip specification. To fully test the circuit, all possible input combinations in every

possible system state should be examined. This is impractical and the number of tests needs to be reduced significantly, yielding potential undiscovered errors.

With *simulation*, a model of the circuit at hand is constructed and simulated. Models are typically provided using hardware description languages such as Verilog or VHDL that are both standardized by IEEE. Based on stimuli, execution paths of the chip model are examined using a simulator. These stimuli may be provided by a user, or by automated means such as a random generator. A mismatch between the simulator's output and the output described in the specification determines the presence of errors. Simulation is like testing, but is applied to models. It suffers from the same limitations, though: the number of scenarios to be checked in a model to get full confidence goes beyond any reasonable subset of scenarios that can be examined in practice.

Simulation is the most popular hardware verification technique and is used in various design stages, e.g., at register-transfer level, gate and transistor level. Besides these error detection techniques, *hardware testing* is needed to find fabrication faults resulting from layout defects in the fabrication process.

### **3.1 MODEL CHECKING**

In software and hardware design of complex systems, more time and effort are spent on verification than on construction. Techniques are sought to reduce and ease the verification efforts while increasing their coverage. Formal methods offer a large potential to obtain an early integration of verification in the design process, to provide more effective verification techniques, and to reduce the verification time.

Let us first briefly discuss the role of formal methods. To put it in

a nutshell, formal methods can be considered as "the applied mathematics for modeling and analyzing ICT systems". Their aim is to establish system correctness with mathematical rigor. Their great potential has led to an increasing use by engineers of formal methods for the verification of complex software and hardware systems. Besides, formal methods are one of the "highly recommended" verification techniques for software development of safety-critical systems according to, e.g., the best practices standard of the IEC (International Electrotechnical Commission) and standards of the ESA (European Space Agency). The resulting report of an investigation by the FAA (Federal Aviation Authority) and NASA (National Aeronautics and Space Administration) about the use of formal methods concludes that

Formal methods should be part of the education of every computer scientist and software engineer, just as the appropriate branch of applied maths is a necessary part of the education of all other engineers.

During the last two decades, research in formal methods has led to the development of some very promising verification techniques that facilitate the early detection of defects. These techniques are accompanied by powerful software tools that can be used to automate various verification steps. Investigations have shown that formal verification procedures would have revealed the exposed defects in, e.g., the Ariane-5 missile, Mars Pathfinder, Intels Pentium II processor, and the Therac-25 therapy radiation machine.

*Model-based* verification techniques are based on models describing the possible system behavior in a mathematically precise and unambiguous manner. It turns out that prior to any form of verification the accurate modeling of systems often leads to the discovery of incompleteness, ambiguities, and inconsistencies in informal system specifications. Such problems are usu-

ally only discovered at a much later stage of the design. The system models are accompanied by algorithms that systematically explore all states of the system model. This provides the basis for a whole range of verification techniques ranging from an exhaustive exploration (model checking) to experiments with a restrictive set of scenarios in the model (simulation), or in reality (testing). Due to unremitting improvements of underlying algorithms and data structures, together with the availability of faster computers and larger computer memories, model-based techniques that a decade ago only worked for very simple examples are nowadays applicable to realistic designs. As the starting point of these techniques is a model of the system under consideration, we have as a given fact that

> Any verification using model-based techniques is only as good as the model of the system.

Model checking is a verification technique that explores all possible system states in a brute-force manner. Similar to a computer chess program that checks possible moves, a model checker, the software tool that performs the model checking, examines all possible system scenarios in a systematic manner. In this way, it can be shown that a given system model truly satisfies a certain property. It is a real challenge to examine the largest possible state spaces that can be treated with current means, i.e., processors and memories. State-of-the-art model checkers can handle state spaces of about  $10^8$  to  $10^9$  states with explicit state-space enumeration. Using clever algorithms and tailored data structures, larger state spaces ( $10^{20}$  up to even  $10^{476}$  states) can be handled for specific problems. Even the subtle errors that remain undiscovered using emulation, testing and simulation can potentially be revealed using model checking.

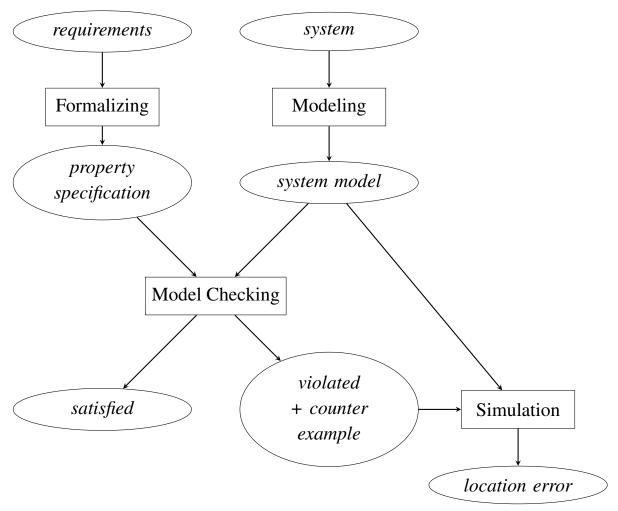

Figure 3.4 Schematic view of the model-checking approach

Typical properties that can be checked using model checking are of a qualitative nature: Is the generated result OK?, Can the system reach a dead-lock situation, e.g., when two concurrent programs are waiting for each other and thus halting the entire system? But also timing properties can be checked: Can a deadlock occur within 1 hour after a system reset?, or, Is a response always received within 8 minutes? Model checking requires a precise and unambiguous statement of the properties to be examined. As with making an accurate system model, this step often leads to the discovery of several ambiguities and inconsistencies in the informal documentation. For instance,

the formalization of all system properties for a subset of the ISDN user part protocol revealed that 55%(!) of the original, informal system requirements were inconsistent.

The system model is usually automatically generated from a model description that is specified in some appropriate dialect of programming languages like C or Java or hardware description languages such as Verilog or VHDL. Note that the property specification prescribes what the system should do, and what it should not do, whereas the model description addresses how the system behaves. The model checker examines all relevant system states to check whether they satisfy the desired property. If a state is encountered that violates the property under consideration, the model checker provides a counterexample that indicates how the model could reach the undesired state. The counterexample describes an execution path that leads from the initial system state to a state that violates the property being verified. With the help of a simulator, the user can replay the violating scenario, in this way obtaining useful debugging information, and adapt the model (or the property) accordingly (see Figure 3.4).

Model checking has been successfully applied to several ICT systems and their applications. For instance, deadlocks have been detected in online airline reservation systems, modern e-commerce protocols have been verified, and several studies of international IEEE standards for in-house communication of domestic appliances have led to significant improvements of the system specifications. Five previously undiscovered errors were identified in an execution module of the Deep Space 1 spacecraft controller, in one case identifying a major design flaw. A bug identical to one discovered by model checking escaped testing and caused a deadlock during a flight experiment 96 million km from earth. In the Netherlands, model checking has revealed several serious design flaws in the control software of a storm surge barrier that protects the main port of Rotterdam against flooding.

# 3.2 CHARACTERISTICS OF MODEL CHECKING

The principles of Model Checking are:

Model checking is an automated technique that, given a finite-state model of a system and a formal property, systematically checks whether this property holds for (a given state in) that model.

# 3.2.1 The Model-Checking Process

In applying model checking to a design the following different phases can be distinguished:

- Modeling phase:

- model the system under consideration using the model description language of the model checker at hand;

- as a first sanity check and quick assessment of the model perform some simulations;

- formalize the property to be checked using the property specification language.

- Running phase: run the model checker to check the validity of the property in the system model.

- Analysis phase:

- property satisfied?  $\rightarrow$  check next property (if any);

- property violated?  $\rightarrow$

- 1. analyze generated counterexample by simulation;

- 2. refine the model, design, or property;

- 3. repeat the entire procedure.

- out of memory?  $\rightarrow$  try to reduce the model and try again.

In addition to these steps, the entire verification should be planned, administered, and organized. This is called *verification organization*. We discuss these phases of model checking in somewhat more detail below.

**Modeling** The prerequisite inputs to model checking are a model of the system under consideration and a formal characterization of the property to be checked.

Models of systems describe the behavior of systems in an accurate and unambiguous way. They are mostly expressed using *finite-state automata*, consisting of a finite set of states and a set of transitions. States comprise information about the current values of variables, the previously executed statement (e.g., a program counter), and the like. Transitions describe how the system evolves from one state into another. For realistic systems, finitestate automata are described using a model description language such as an appropriate dialect/extension of C, Java, VHDL, or the like.

In order to improve the quality of the model, a simulation prior to the model checking can take place. Simulation can be used effectively to get rid of the simpler category of modeling errors. Eliminating these simpler errors before any form of thorough checking takes place may reduce the costly and time-consuming verification effort.

To make a rigorous verification possible, properties should be described in a precise and unambiguous manner. This is typically done using a property specification language. We focus in particular on the use of a *temporal logic* as a property specification language, a form of modal logic that is appropriate to specify relevant properties of ICT systems. In terms of mathematical logic, one checks that the system description is a model of a temporal logic formula. This explains the term "model checking". Temporal logic is basically an extension of traditional propositional logic with operators that refer to the behavior of systems over time. It allows for the specification of a broad range of relevant system properties such as functional correctness (does the system do what it is supposed to do?), reachability (is it possible to end up in a deadlock state?), safety ("something bad never happens"), liveness ("something good will eventually happen"), fairness (does, under certain conditions, an event occur repeatedly?), and real-time properties (is the system acting in time?).

Although the aforementioned steps are often well understood, in practice it may be a serious problem to judge whether the formalized problem statement (model + properties) is an adequate description of the actual verification problem. This is also known as the validation problem. The complexity of the involved system, as well as the lack of precision of the informal specification of the systems functionality, may make it hard to answer this question satisfactorily. Verification and validation should not be confused. Verification amounts to check that the design satisfies the requirements that have been identified, i.e., verification is "check that we are building the thing right". In validation, it is checked whether the formal model is consistent with the informal conception of the design, i.e., validation is "check that we are verifying the right thing". **Running the Model Checker** The model checker first has to be initialized by appropriately setting the various options and directives that may be used to carry out the exhaustive verification. Subsequently, the actual model checking takes place. This is basically a solely algorithmic approach in which the validity of the property under consideration is checked in all states of the system model.

**Analyzing the Results** There are basically three possible outcomes: the specified property is either valid in the given model or not, or the model turns out to be too large to fit within the physical limits of the computer memory.

In case the property is valid, the following property can be checked, or, in case all properties have been checked, the model is concluded to possess all desired properties.

Whenever a property is falsified, the negative result may have different causes. There may be a *modeling error*, i.e., upon studying the error it is discovered that the model does not reflect the design of the system. This implies a correction of the model, and verification has to be restarted with the improved model. This reverification includes the verification of those properties that were checked before on the erroneous model and whose verification may be invalidated by the model correction! If the error analysis shows that there is no undue discrepancy between the design and its model, then either a *design error* has been exposed, or a *property error* has taken place. In case of a design (together with its model) has to be improved. It may be the case that upon studying the exposed error it is discovered that the property does not reflect the informal requirement that had to be validated. This implies a modification of the property, and a new verification of the model has to be

carried out. As the model is not changed, no reverification of properties that were checked before has to take place. The design is verified if and only if all properties have been checked with respect to a valid model.

Whenever the model is too large to be handled - state spaces of real-life systems may be many orders of magnitude larger than what can be stored by currently available memories - there are various ways to proceed. A possibility is to apply techniques that try to exploit implicit regularities in the structure of the model. Examples of these techniques are the representation of state spaces using symbolic techniques such as binary decision diagrams or partial order reduction. Alternatively, rigorous abstractions of the complete system model are used. These abstractions should preserve the (non-)validity of the properties that need to be checked. Often, abstractions can be obtained that are sufficiently small with respect to a single property. In that case, different abstractions need to be made for the model at hand. Another way of dealing with state spaces that are too large is to give up the precision of the verification result. The probabilistic verification approaches explore only part of the state space while making a (often negligible) sacrifice in the verification coverage.

**Verification Organization** The entire model-checking process should be well organized, well structured, and well planned. Industrial applications of model checking have provided evidence that the use of version and configuration management is of particular relevance. During the verification process, for instance, different model descriptions are made describing different parts of the system, various versions of the verification models are available (e.g., due to abstraction), and plenty of verification parameters (e.g., model-checking options) and results (diagnostic traces, statistics) are available. This

information needs to be documented and maintained very carefully in order to manage a practical model-checking process and to allow the reproduction of the experiments that were carried out.

# 3.2.2 Strengths and Weaknesses

The strengths of model checking are:

- It is a general verification approach that is applicable to a wide range of applications such as embedded systems, software engineering, and hardware design.

- It supports *partial verification*, i.e., properties can be checked individually, thus allowing focus on the essential properties first. No complete requirement specification is needed.

- It is not vulnerable to the likelihood that an error is exposed; this contrasts with testing and simulation that are aimed at tracing the most probable defects.

- It provides *diagnostic information* in case a property is invalidated; this is very useful for debugging purposes.

- It is a potential "push-button" technology; the use of model checking requires neither a high degree of user interaction nor a high degree of expertise.

- It enjoys a rapidly increasing *interest by industry*; several hardware companies have started their in-house verification labs, job offers with required skills in model checking frequently appear, and commercial model checkers have become available.

- It can be easily *integrated* in existing development cycles; its learning curve is not very steep, and empirical studies indicate that it may lead to shorter development times.

- It has a *sound and mathematical underpinning*; it is based on theory of graph algorithms, data structures, and logic.

The weaknesses of model checking are:

- It is mainly appropriate to *control-intensive* applications and less suited for data-intensive applications as data typically ranges over infinite domains.

- Its applicability is subject to *decidability issues*; for infinite-state systems, or reasoning about abstract data types (which requires undecidable or semi-decidable logics), model checking is in general not effectively computable.